Automated Design of Hardware

Research Overview

In dedicated hardware development using ASICs or FPGAs for implementing complex algorithms such as pairing operations, it is expected that utilizing parallelism will result in low power consumption and low latency compared to software implementation on general-purpose CPUs. However, there is a need to consider architectures suitable for algorithms and data dependencies in parallel processing, which leads to significant human and time costs in development. Therefore, we are shortening the design time by automating the generation of parallel processing scheduling. Additionally, we are researching the implementation of high-level synthesis methods using Python descriptions with libraries such as NumPy to support more abstract designs.

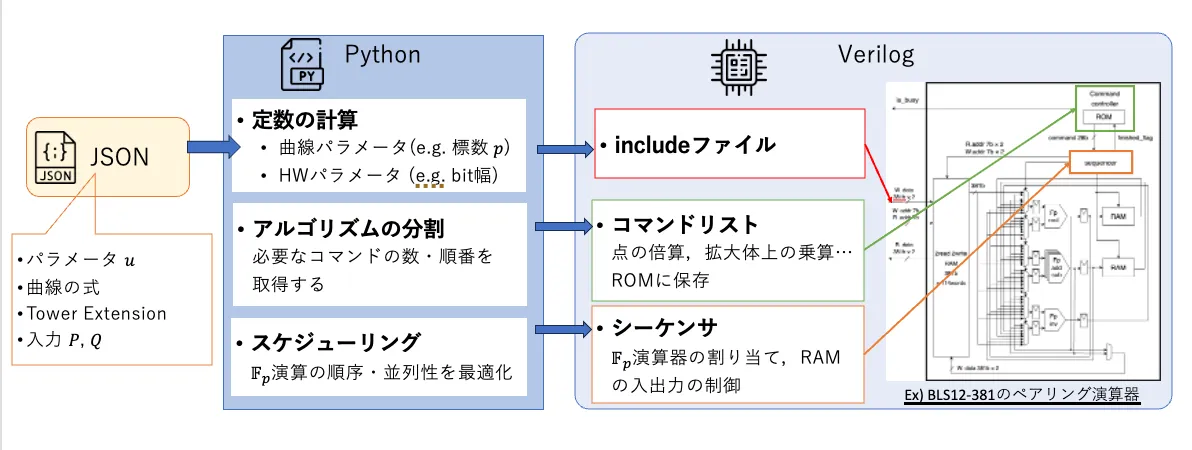

Automated Design Method for Pairing Operations

Pairing operations are gaining attention in recent years as they can be applied to advanced cryptographic functions such as ID-based, attribute-based, and searchable encryption. Pairing operations require a significant amount of computation time, thus demanding high-performance hardware accelerators. However, hardware design usually takes a considerable amount of time. This research aims to establish an automated design method using pre-designed architectural templates. By applying this method to various curves and comparing conditions such as security level, latency, and chip area, we aim to help select the most suitable curve for pairing hardware.

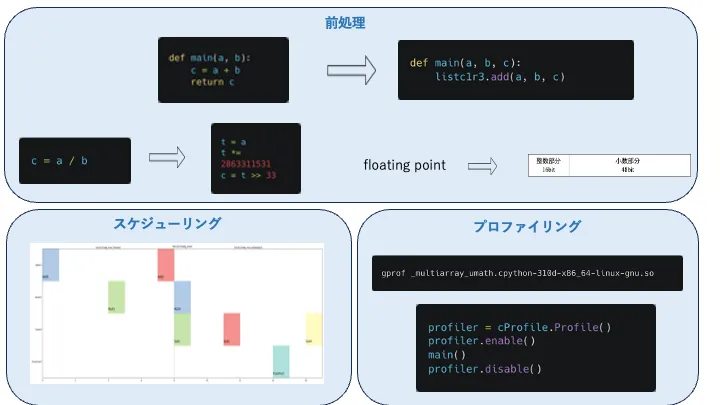

Examination of High-Level Synthesis Methods

With the increasing complexity of LSI design, high-level synthesis, which allows design at the operational description level using programming languages, is gaining attention. To enable high-level abstract designs, it is necessary to handle Python, but currently available compilers for Python are specialized for AI, with limitations such as inability to handle libraries. Since Python is predominantly used with libraries like NumPy, supporting these is essential for enabling more abstract designs. This research aims to implement high-level synthesis methods using Python descriptions with libraries. Furthermore, incorporating profiling during the design into the high-level synthesis process is also being conducted.