ハードウェアの自動設計

研究概要

ペアリング演算などの複雑なアルゴリズムを実装する際,ASICやFPGAを用いた専用ハードウェア開発では,汎用CPU上でソフトウェア実装を行った場合と比較して,並列性を活用することで低消費電力・低レイテンシでの処理が期待されます.一方,アルゴリズムに適したアーキテクチャやデータの依存性を考慮した並列処理を検討する必要があるため,開発に膨大な人的・時間的なコストがかかるという問題があります.そこで,我々は並列処理のスケジューリングを自動生成することで設計時間の短縮を行っています.また,より抽象度の高い設計に対応するため,NumPyなどのライブラリを用いたPython記述の高位合成手法の実装の研究も行っています.

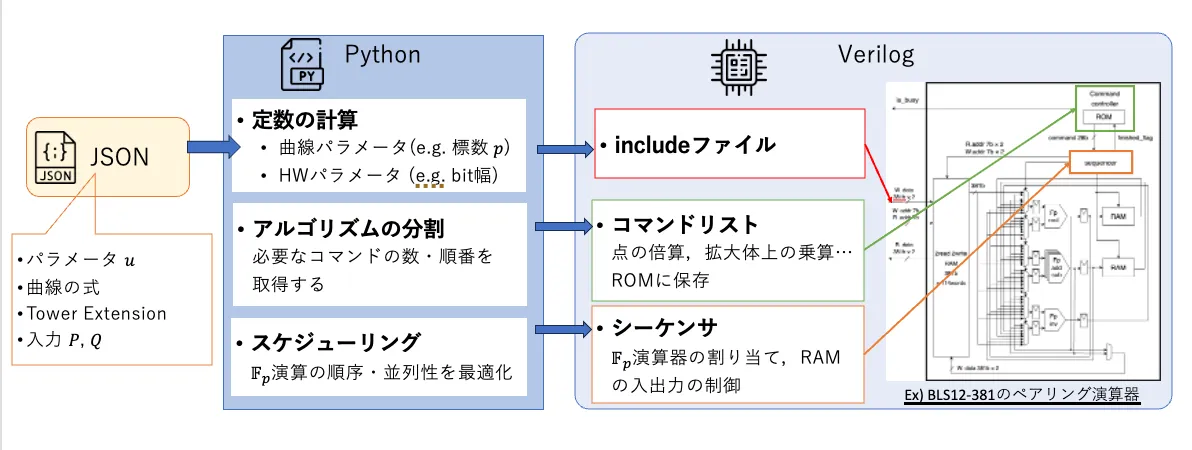

ペアリング演算の自動設計手法

ペアリング演算は,IDベース暗号・属性ベース暗号・検索可能暗号などの高機能暗号に応用できるため,近年注目を集めています.ペアリング演算には非常に多くの計算時間がかかるため,高性能なハードウェアアクセラレータが求められます.しかしながら,ハードウェアの設計には通常膨大な時間がかかります.そこで本研究では,予め設計したアーキテクチャのテンプレートを用いた自動設計手法の確立を目指しています.さらにこの手法をいくつかの曲線に適用し,セキュリティレベル・レイテンシ・チップの面積などの条件を比較することで,ペアリングハードウェアに最適な曲線の選択に役立てることを目指しています.

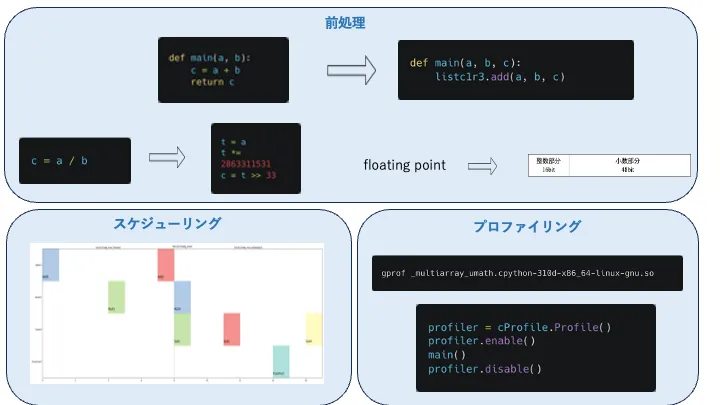

高位合成手法の検討

LSI設計の複雑化に伴い,プログラミング言語を用いて動作記述レベルでの設計が可能な高位合成が注目されています.抽象度の高い設計を可能にするにはPythonを扱う必要がありますが,現在Pythonを扱えるコンパイラはAIに特化している,ライブラリを扱えない等の問題点があります.PythonではAI以外にもNumPyなどのライブラリを用いて記述することがほとんどであり,より抽象度の高い設計を可能とするにはこれらへの対応が必要です.この研究ではライブラリを用いたPython記述の高位合成手法の実装を目指します.また,設計の際のプロファイリングを高位合成のプロセスに組み込むことも行います.